12. Transistor nMOS - efeitos da redução das dimensões

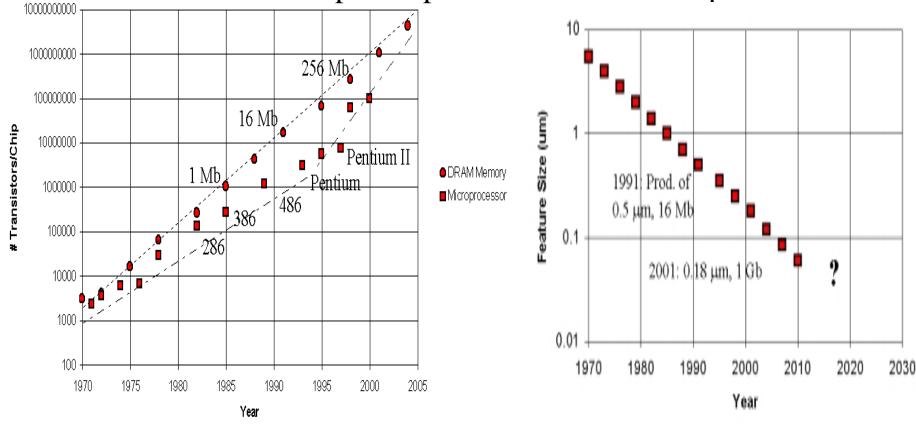

# Tendência da redução das dimensões

• Lei de Moore: O número de transistores no CI dobra a cada 18 meses

Consequências: - O custo de uma fábrica de IC dobra a cada 3 anos;

- A dimensão mínima (L) diminui 40 % a cada 3 anos;

- O custo por dispositivo diminui 24% por ano.

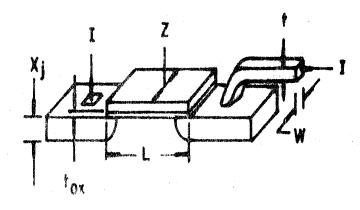

## Leis de escalamento de dispositivos

|                                      | Campo     | Tensão    |

|--------------------------------------|-----------|-----------|

|                                      | constante | constante |

| $\overline{L, Z, t, W, x_j, t_{ox}}$ | 1/k       | 1/k       |

| Tensão $V_{dd}$ , $V_{t}$            | 1/k       | 1         |

| Corrente I                           | $1/k^{2}$ | k         |

| Potência IV                          | 1/k       | k         |

| Atraso por porta CV/I                | 1/k       | $1/k^2$   |

| Produto atraso-pot. CV <sup>2</sup>  | $1/k^3$   | 1/k       |

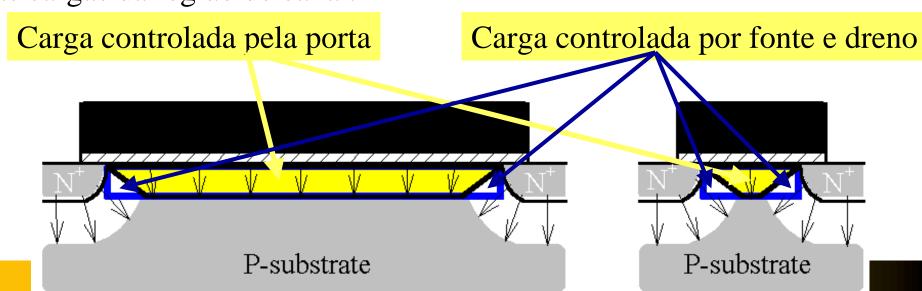

### Efeitos de canal curto

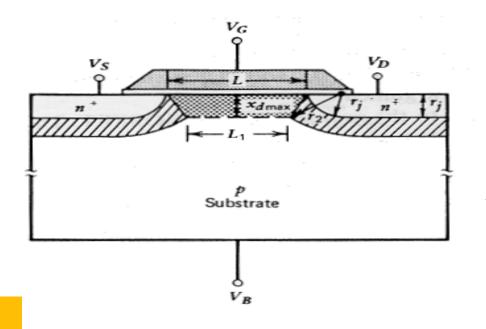

■ São efeitos decorrentes da diminuição do comprimento do canal (L) dos transistores. Em transistores de canal longo praticamente todas as cargas da região do canal são controladas pela porta. A situação de canal curto é configurada quando a quantidade de carga controlada pela porta é da mesma ordem de grandeza que a presente nas regiões de depleção de fonte e dreno. Nesta situação a porta já não controla todas as cargas da região de canal.

# Redução de V<sub>T</sub>

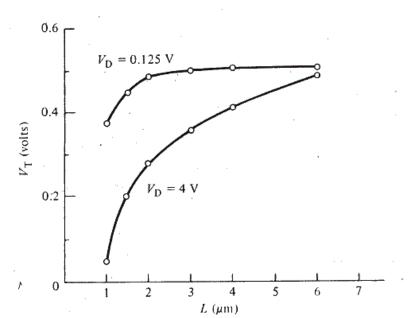

Uma consequência direta da redução do canal do transistor MOS é a redução da tensão de limiar, devido à redução da carga controlada pela porta.

$$\Delta V_T = V_T(curto) - V_T(longo)$$

$$\Delta V_T = V_T(curto) - V_T(longo) \quad \Delta V_T = -\frac{qN_A x d_{\max} r_j}{C_{ox} L} \left( \sqrt{1 + \frac{2x d_{\max}}{r_j}} - 1 \right)$$

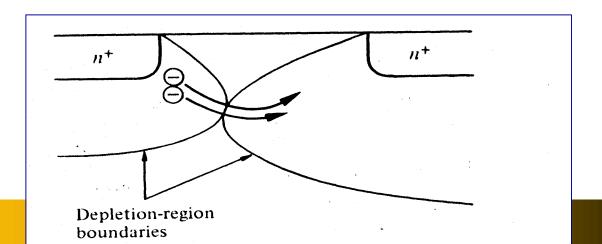

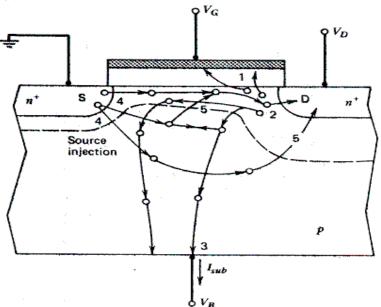

# • Efeito de perfuração (punch-through)

Outra consequência da redução do canal do transistor MOS esta relacionada pela proximidade das regiões de depleção de fonte e dreno comcomitantemente com o aumento do potencial  $(V_{DS})$  aplicado na região de dreno, provocando uma diminuição da barreira de potencial da junção canal-fonte (DIBL - Drain Induced Barrier Lowering).

Neste caso aparece uma corrente ( $I_{DS}\alpha V_{DS}^2/L^3$ ) fluindo não mais pelo canal do transistor e sim pelo "corpo" do mesmo. Este efeito chama-se perfuração do transistor ou punch-through).

#### CRITÉRIO DE SALLY LIU

– Defini-se tensão de perfuração  $(V_{PT})$  ao potencial  $(V_{DS})$  aplicado ao dreno de um transistor de canal (L) e largura (W) no qual temse uma corrente  $(I_{DS})$  tal que

$$I_{DS} = 10^{-9} \frac{W}{L}$$

na condição de polarização:

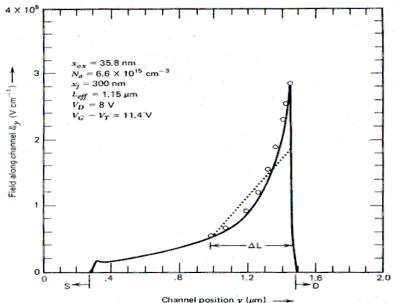

### • Efeito de elétrons energéticos ("hot electrons")

Outra consequência da redução do canal do transistor MOS esta relacionada com o aumento do campo elétrico, principalmente junto ao dreno. Este elevado campo elétrico (MV/cm) induz elétrons energéticos ("hot electrons") a ionizarem, por impacto, portadores na região de canal. Uma das consequências desta ionização é a alteração da tensão de limiar  $(V_T)$  com o tempo, pela captura destes elétrons energéticos pelo óxido de porta.

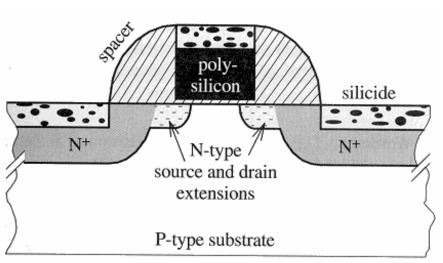

#### ESTRUTURA LDD (LIGHTLY DOPED DRAIN)

A estrutura LDD representa uma solução para minimizar os problemas decorrentes do elevado campo elétrico junto ao dreno do transistor MOS. O campo elétrico numa junção PN é função, além do potencial aplicado, das concentrações dos materiais que a compõe. Deste modo, para reduzir-se o campo elétrico deve-se reduzir a concentração das junções.

$$E(x, y) = \frac{1}{\varepsilon_{Si}} \iint \rho(x, y) dx dy$$

Ao se reduzir as concentrações de fonte e dreno, resulta na elevação da resistência série associada ao dispositivo. Na estrutura LDD, cria-se uma extensão das regiões de fonte e dreno, porém menos dopadas. O comprimento destas regiões devem ser projetado de modo a incrementar o

menos possível a resistência série.

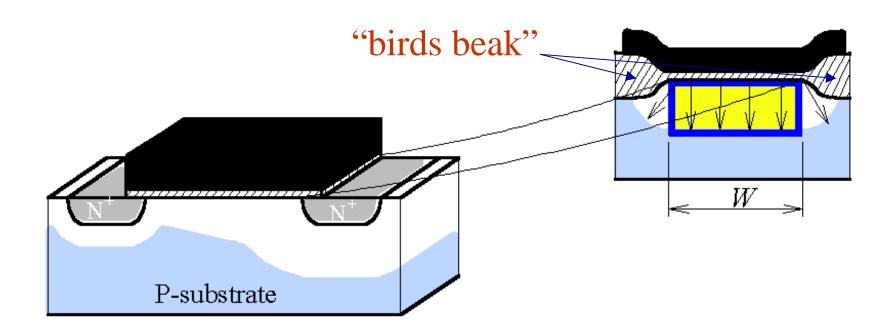

### Efeitos de canal estreito

• Com a diminuição da largura do canal dos transistores MOS, a região de carga controlada pela porta sofre um aumento, devido à região situada abaixo do óxido de campo ("birds beak").

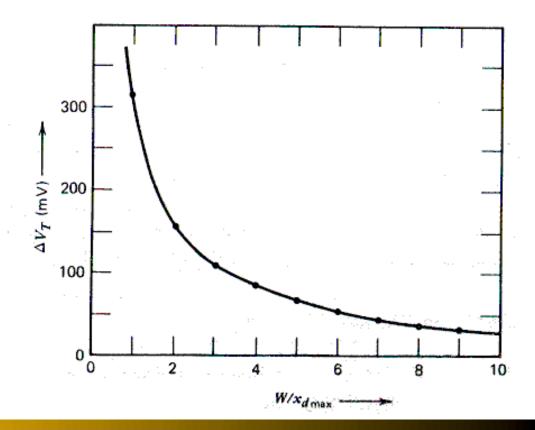

### Aumento de V<sub>T</sub>

Como a tensão de limiar do transistor é proporcional à quantidade de carga controlada pela porta, em transistores de canal estreito tem-se uma elevação da tensão de limiar.

$$\Delta V_T = \frac{\pi q N_a (x_{dmax})^2}{2C_{ox}W}$$